开个新坑,记录游戏《图灵完备》的完整通关流程。

《图灵完备》是一款电路模拟器(确信),游戏内容是从门电路开始设计,直到搭建完成自己的计算机,并编写汇编语言程序完成对应挑战。

(目前已经通关了嘿嘿嘿嘿嘿,如果这个系列反响好的话就出下一期)

UP是计科专业的,计算机组成原理课程几乎满分过(10进制转16进制算错了扣1分),所以计算机体系结构设计没啥大问题,但是数电挺烂的,所以电路图肯定很丑,大佬们轻喷TAT

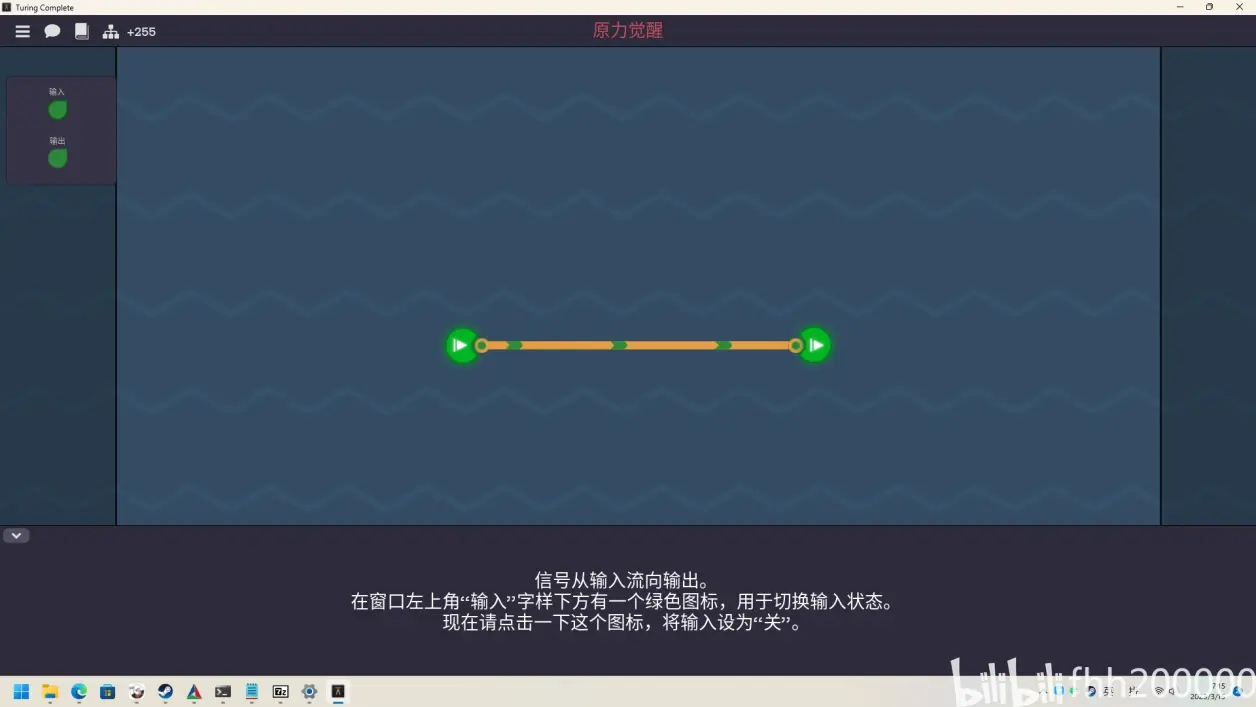

原力觉醒

如图1.1所示。

本关只需要把输入和输出连接起来,并切换左边的输入状态即可。

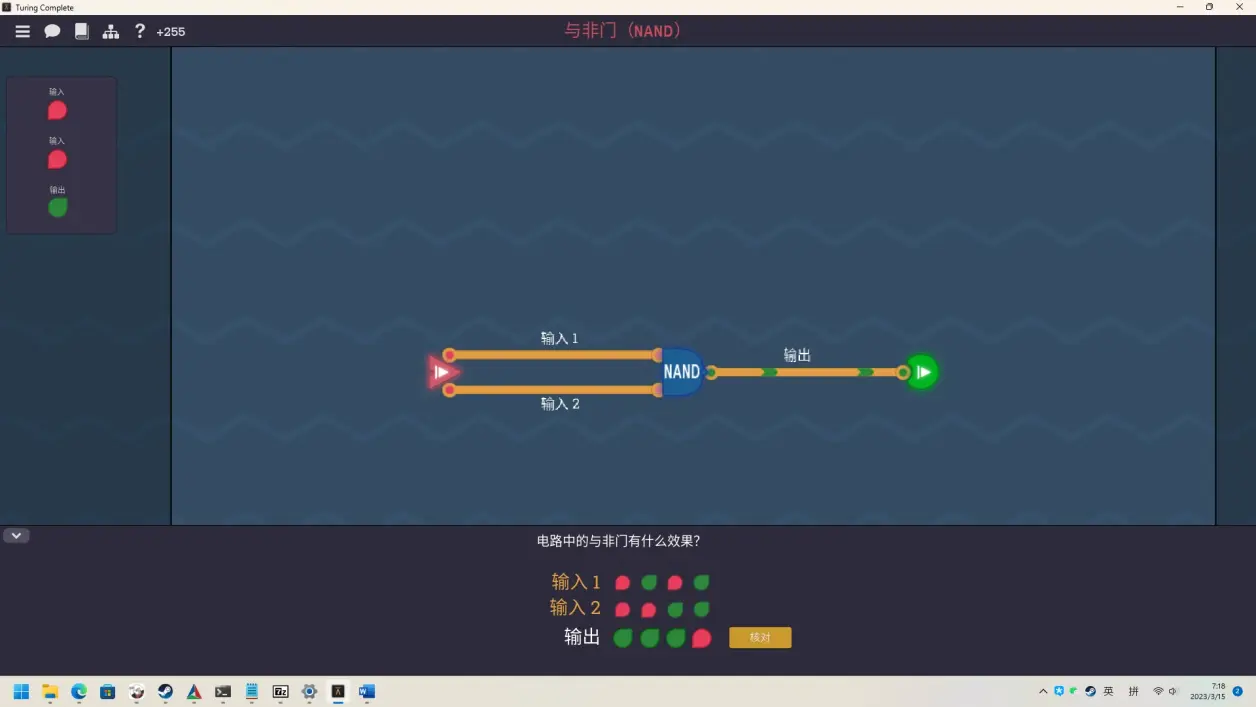

与非门(NAND)

如图1.2所示。本关引入了“真值表”的概念。在数字电路学科中,真值表一般用于列出一个电路的所有确定的状态。在实际状态分析的时候(以及考试的时候),用“1”代表信号为“真/存在/有效”,用“0”代表信号为“假/不存在/无效”。(因为很显然不可能每次画图的时候都带着红笔和绿笔23333)

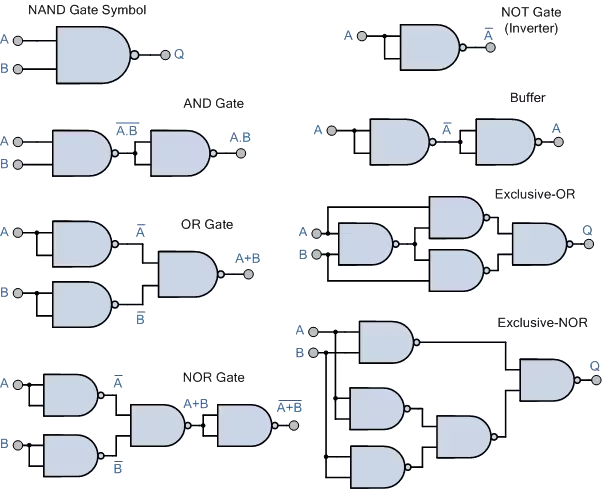

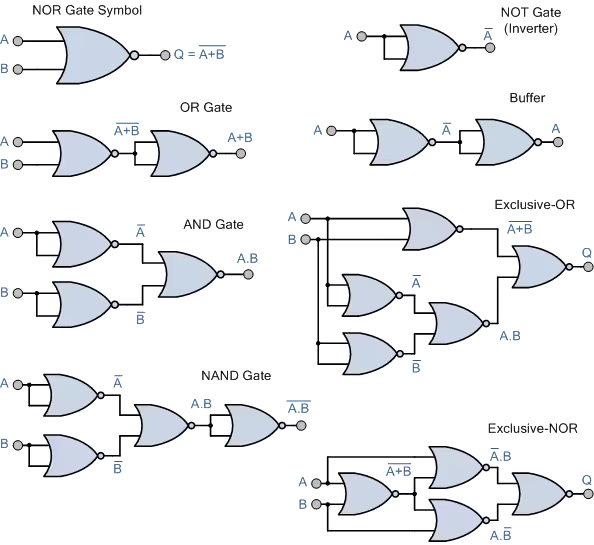

为什么第一个接触的门电路是NAND呢?因为人们相信,使用NAND门可以推导出其他任意一种门电路,所以被称为“通用逻辑门”(Universal Logic Gates)。

(其实NAND和NOR两种门电路都是“通用逻辑门”,如图1.3、图1.4所示。UP不是电子专业的学生,所以并不能确定为啥游戏选了NAND……大概是因为现实生活中NAND的占地更小、成本更低,所以使用广泛?)

本关要求写出NAND门的真值表。从其名称“与非”中不难发现,其逻辑为“先与再非”,即:当两者输入均为1时,输出0;其余情况下均为1。逻辑表达式为。

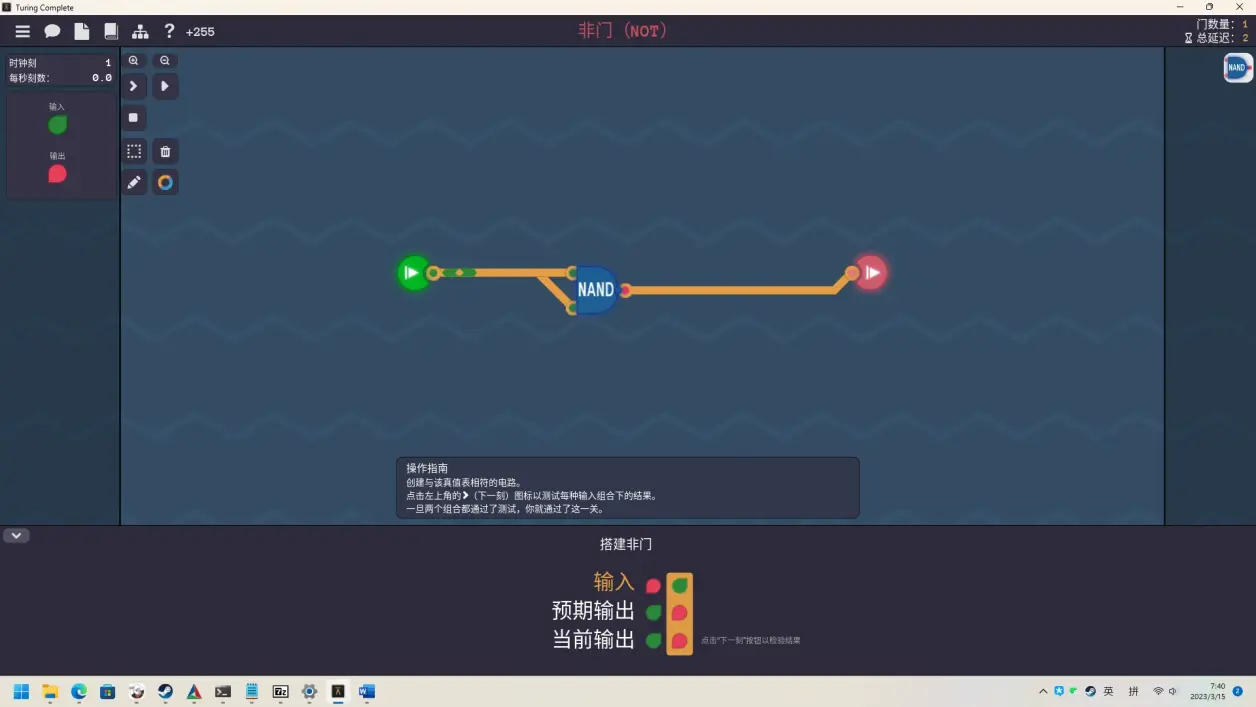

非门(NOT)

如图1.5所示。只需将输入信号同时接入NAND的输入端即可。逻辑表达式为。

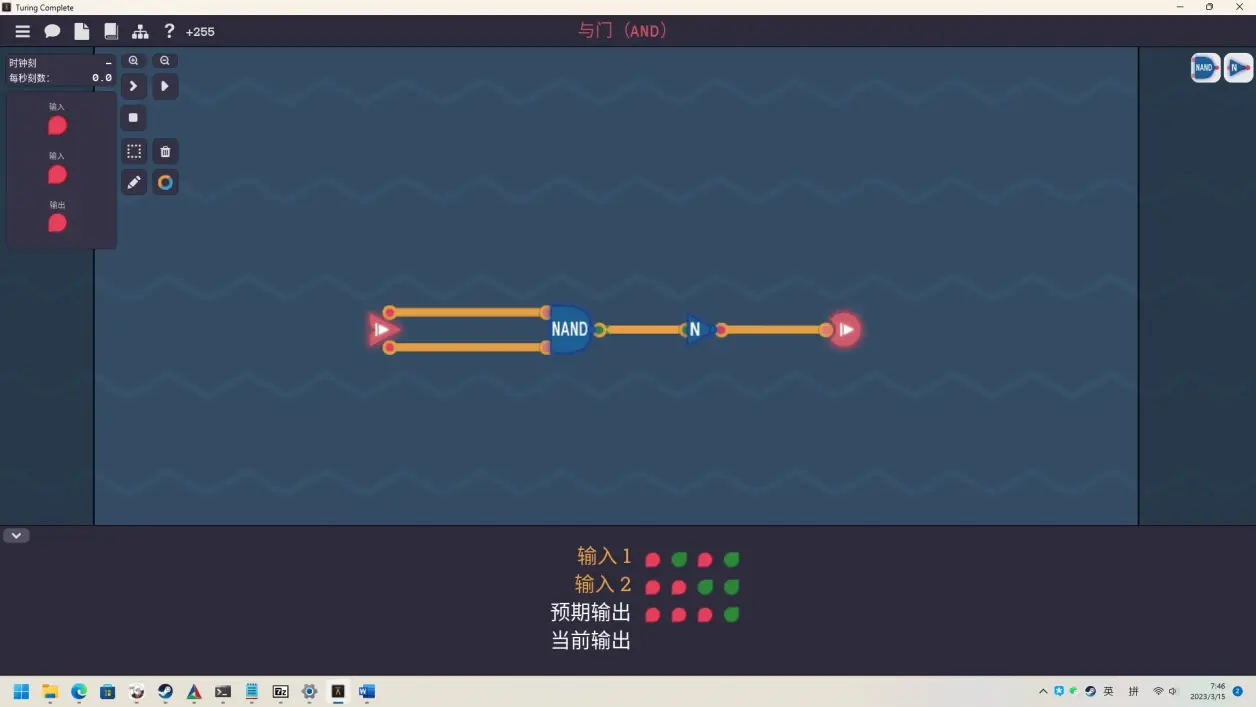

与门(AND)

如图1.6所示,只需将NAND的输出再通过一次非门即可。逻辑表达式为 。

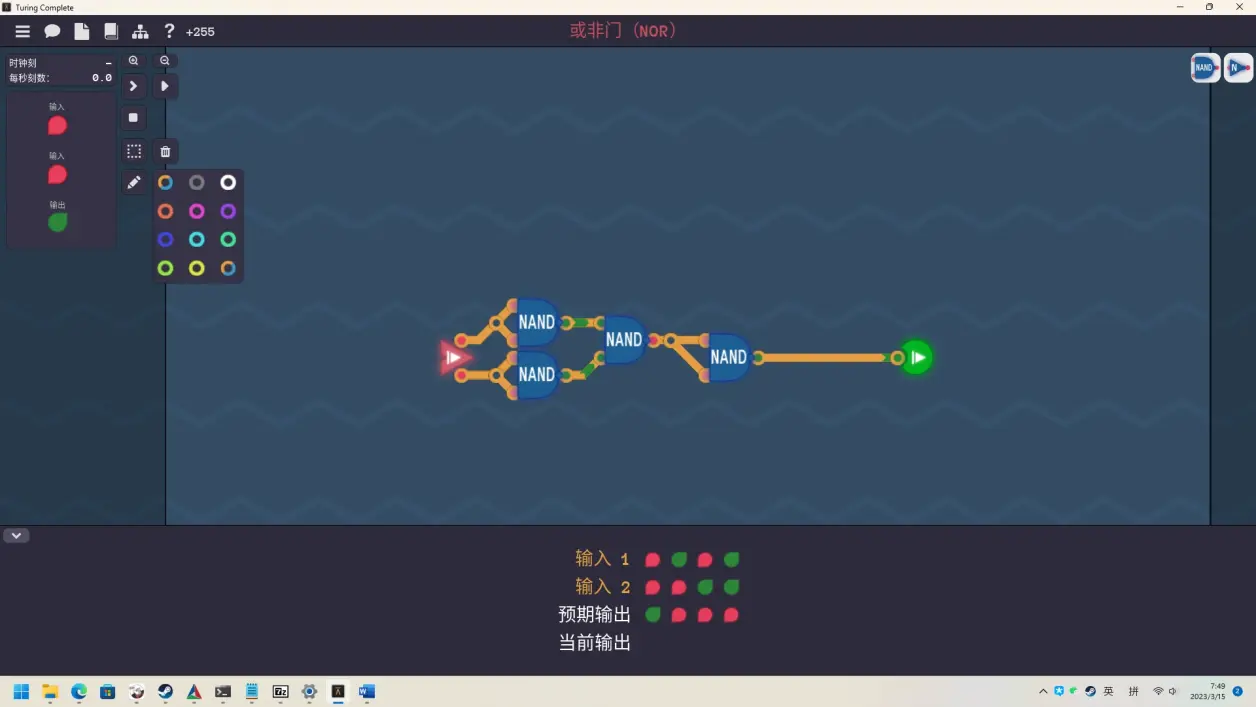

或非门(NOR)

如图1.7所示。使用4个NAND门搭建NOR门。逻辑表达式为。

(注:此处使用“德·摩根定律”化简了)。

图1.7 或非门(NOR)

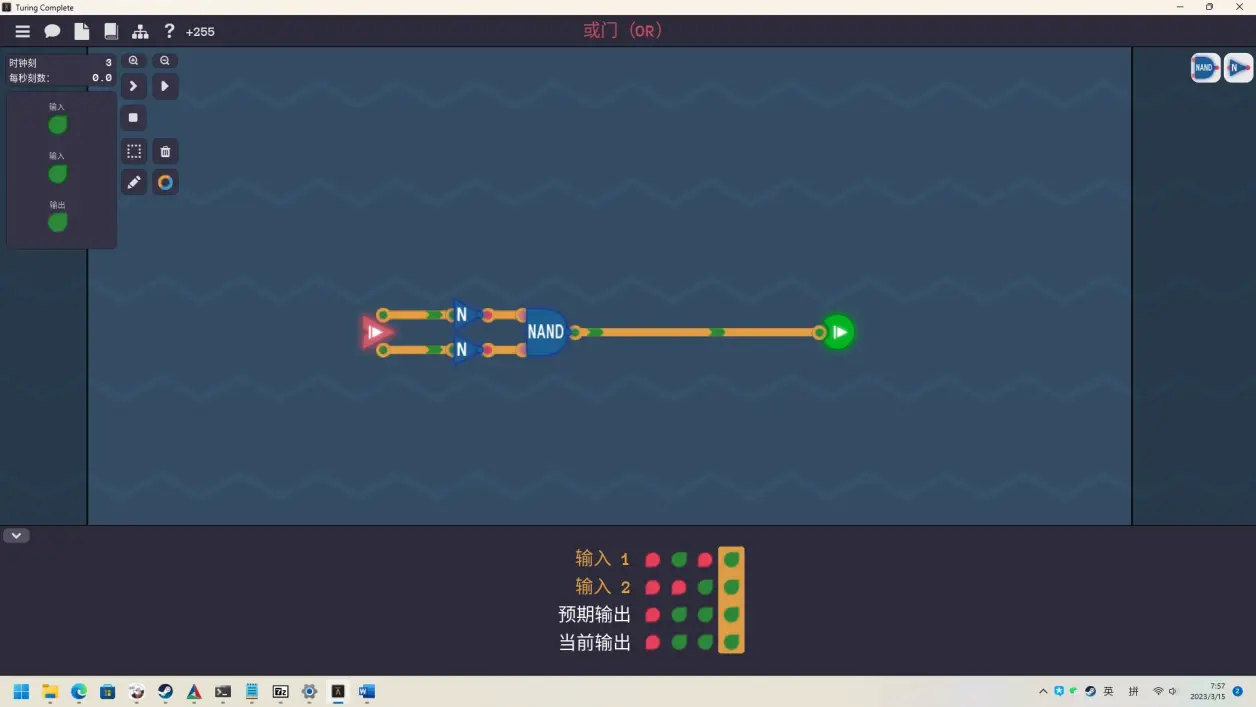

或门(OR)

如图1.8所示,只需将NAND的输入通过一次非门即可。逻辑表达式为。

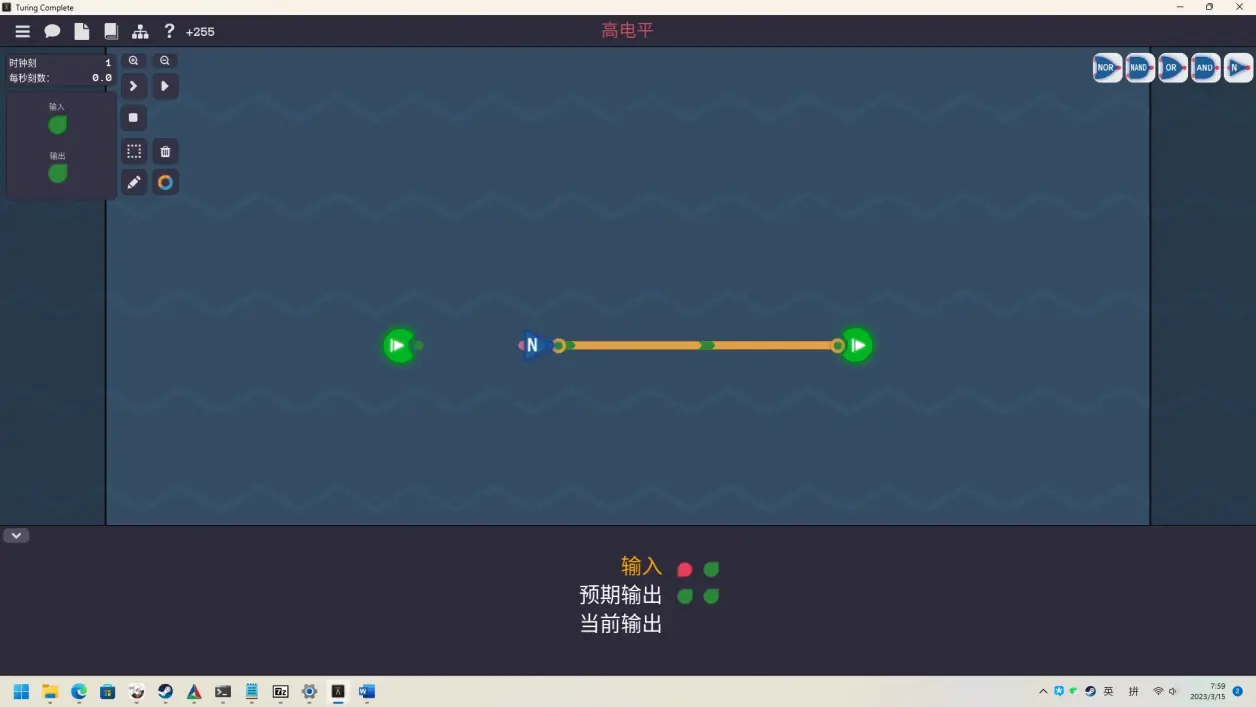

高电平

如图1.9所示,只需将非门的输出连接,保留非门的输入空置。

在现实生活中的电路设计,保持门电路的引脚空置可能会引入不确定性因素(电磁波干扰等)。一般情况下输入脚将会被接地,以确保输入是“0”。

第二刻

如图1.10所示。该电路要求仅在“输入1为1,输入2为0”时输出1。逻辑表达式为。

异或门(XOR)

如图1.11所示。使用4个NAND门搭建时将会解锁成就“4 NAND = XOR”。逻辑表达式为。

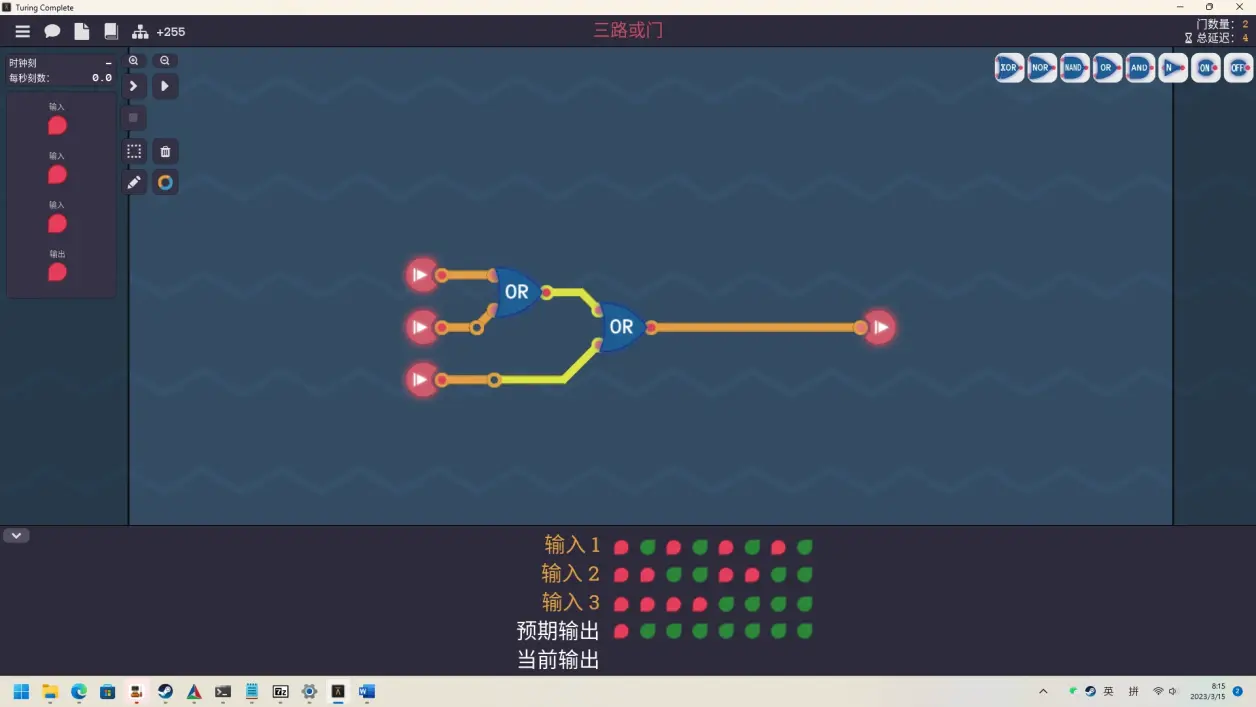

三路或门

如图3.12所示。逻辑表达式为。

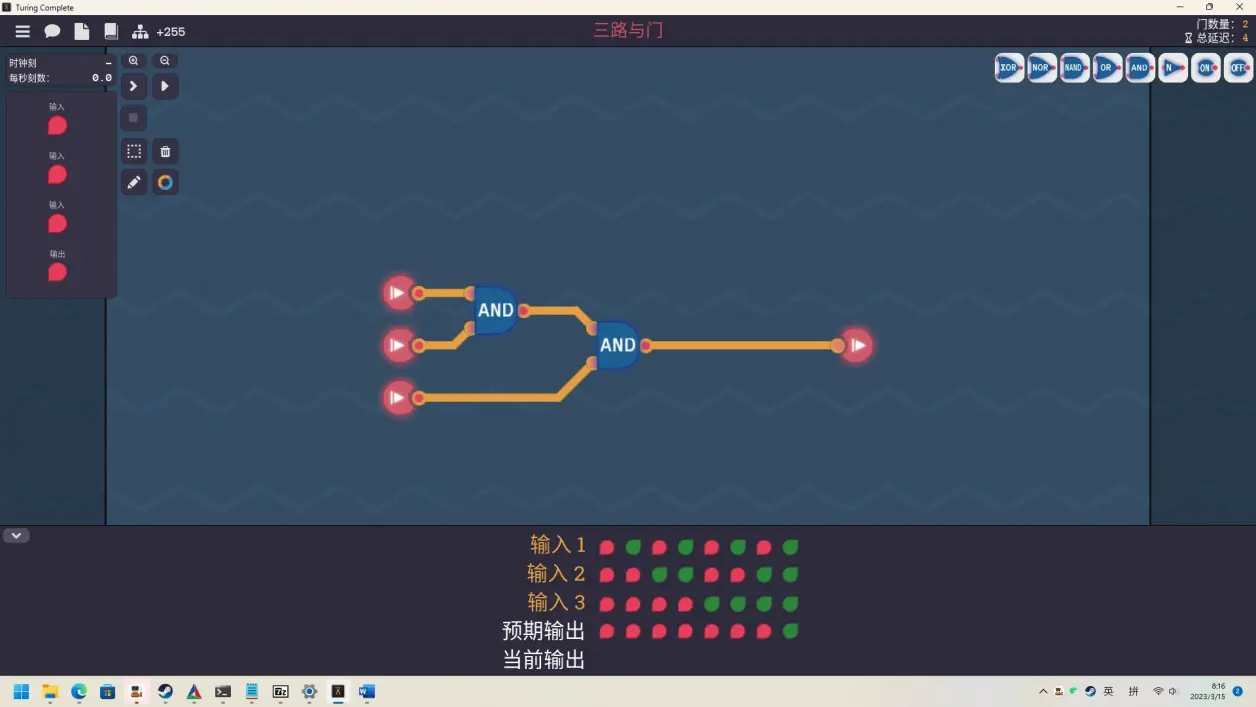

三路与门

如图3.13所示。逻辑表达式为。

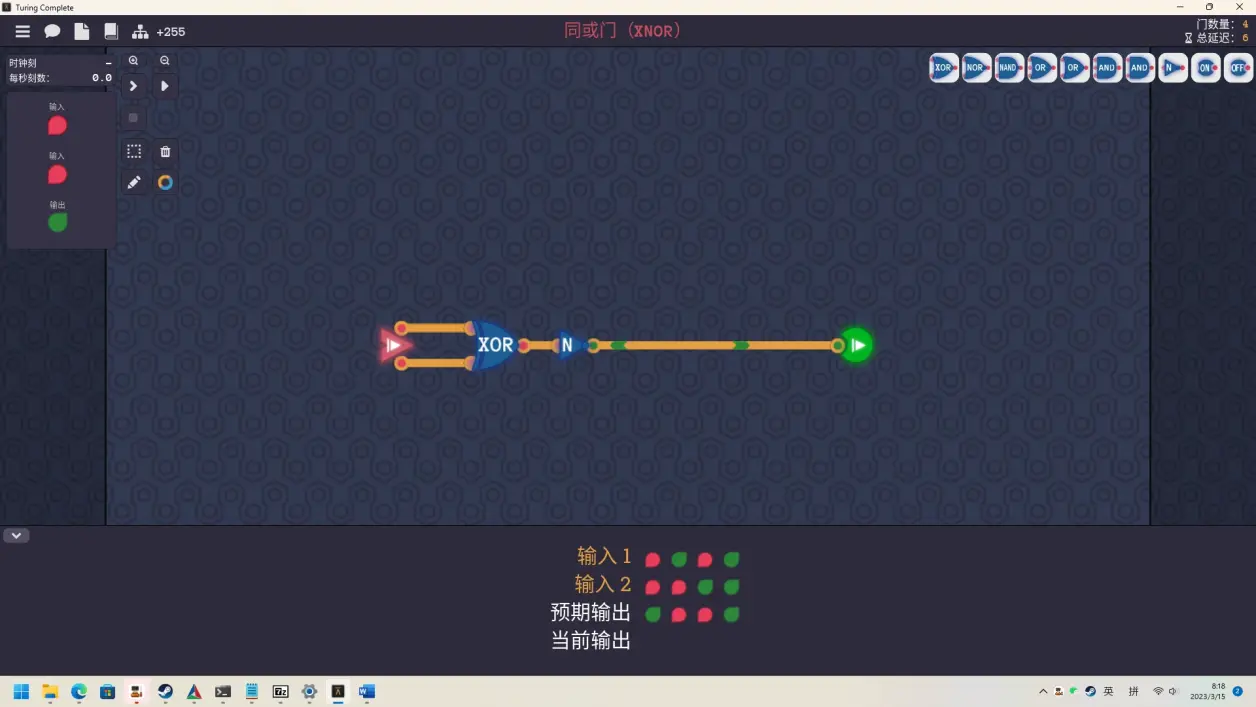

同或门

如图3.14所示。将XOR门输出接入非门即可。逻辑表达式为。