本题链接:

https://hdlbits.01xz.net/wiki/Fsm2s

这是一个具有两个状态、两个输入和一个输出的Moore 型状态机。

实现这个状态机。

此练习与 fsm2 相同,但使用了同步复位。

题目

module top_module(

input clk,

input reset, // Synchronous reset to OFF

input j,

input k,

output out);提示:

是的,比起使用有限状态机这里还有好几种方法来实现功能。但是这不是我们这个练习的重点。

提示:

这是一个JK触发器。

答案

module top_module(

input clk,

input reset, // Synchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

case (state)

module top_module(

input clk,

input reset, // Synchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

case (state)

ON: next_state <= k ? OFF : ON;

OFF: next_state <= j ? ON : OFF;

endcase

end

always @(posedge clk) begin

if (reset)

state <= OFF;

else

state <= next_state;

end

assign out = (state == ON);

endmodule

ON: next_state <= k ? OFF : ON;

OFF: next_state <= j ? ON : OFF;

endcase

end

always @(posedge clk) begin

if (reset)

state <= OFF;

else

state <= next_state;

end

assign out = (state == ON);

endmodule

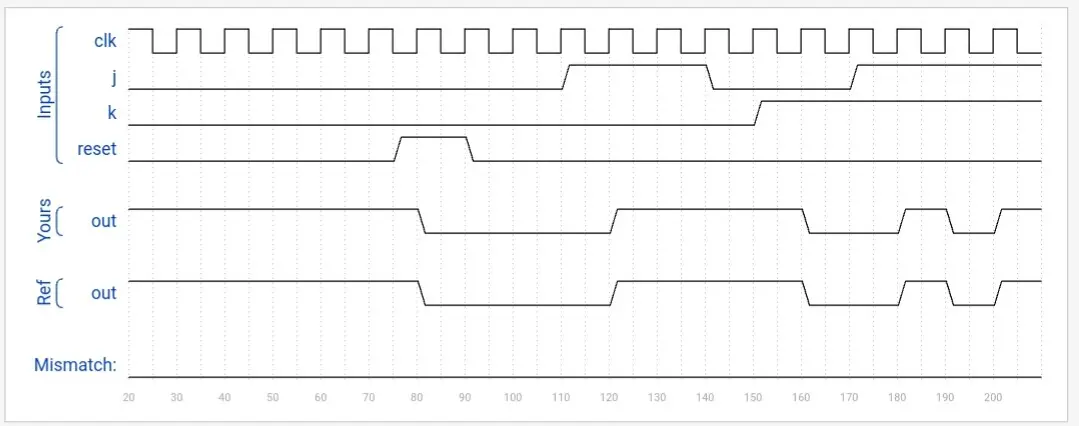

输出波形

有限状态机(Finite-State Machine,FSM),简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。状态机不仅是一种电路的描述工具,而且也是一种思想方法,在电路设计的系统级和 RTL 级有着广泛的应用。

Verilog 中状态机主要用于同步时序逻辑的设计,能够在有限个状态之间按一定要求和规律切换时序电路的状态。状态的切换方向不但取决于各个输入值,还取决于当前所在状态。状态机可分为 2 类:Moore 状态机和 Mealy 状态机。

3段式状态机设计如下:

首先,根据状态机的个数确定状态机编码。利用编码给状态寄存器赋值,代码可读性更好。

状态机第一段,时序逻辑,非阻塞赋值,传递寄存器的状态。

状态机第二段,组合逻辑,阻塞赋值,根据当前状态和当前输入,确定下一个状态机的状态。

状态机第三段,时序逻辑,非阻塞赋值,根据当前状态和当前输入,确定输出信号。

为确保系统上电后有一个明确、稳定的初始状态,或系统运行状态紊乱时可以恢复到正常的初始状态,数字系统设计中一定要有复位电路模块。复位电路异常可能会导致整个系统的功能异常,所以在一定程度上,复位电路的重要性也不亚于时钟电路。

复位电路可分类为同步复位和异步复位。

同步复位

同步复位是指复位信号在时钟有效边沿到来时有效。如果没有时钟,无论复位信号怎样变化,电路也不执行复位操作。

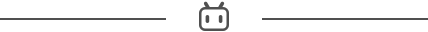

同步复位常常会被综合成如下电路:

同步复位的优点:信号间是同步的,能滤除复位信号中的毛刺,有利于时序分析。

同步复位的缺点:大多数触发器单元是没有同步复位端的,采用同步复位会多消耗部分逻辑资源。且复位信号的宽度必须大于一个时钟周期,否则可能会漏掉复位信号。

异步复位

异步复位是指无论时钟到来与否,只要复位信号有效,电路就会执行复位操作。

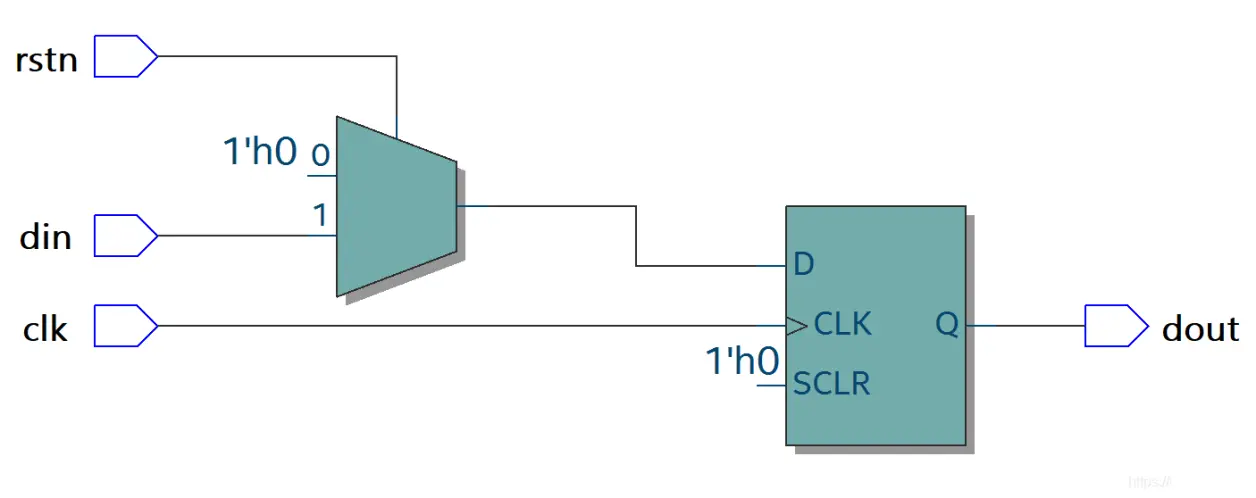

异步复位常常会被综合成如下电路:

异步复位的优点:大多数触发器单元有异步复位端,不会占用额外的逻辑资源。且异步复位信号不经过处理直接引用,设计相对简单,信号识别快速方便。

异步复位的缺点:复位信号与时钟信号无确定的时序关系,异步复位很容易引起时序上 removal 和 recovery 的不满足。且异步复位容易受到毛刺的干扰,产生意外的复位操作。

参考内容:

5.1 Verilog 复位简介 | 菜鸟教程:

https://www.runoob.com/w3cnote/verilog2-reset.html

6.3 Verilog 状态机 | 菜鸟教程:

https://www.runoob.com/w3cnote/verilog-fsm.html